Phase Shift Keying (PSK) es la técnica de modulación digital en la que la fase de la señal portadora se cambia variando las entradas de seno y coseno en un momento determinado. La técnica PSK se utiliza ampliamente para las redes LAN inalámbricas, la biométrica, las operaciones sin contacto, junto con las comunicaciones RFID y Bluetooth.

PSK es de dos tipos, dependiendo de las fases en que se desplaza la señal. Son –

Clave de cambio de fase binaria (BPSK)

También se denomina PSK bifásico o clave de inversión de fase. En esta técnica, la portadora sinusoidal toma dos inversiones de fase, como 0° y 180°.

BPSK es básicamente un esquema de modulación de doble banda lateral suprimida (DSBSC), para que el mensaje sea la información digital.

Codificación por desplazamiento de fase en cuadratura (QPSK)

Esta es la técnica de codificación por desplazamiento de fase, en la que la portadora sinusoidal toma cuatro inversiones de fase, como 0°, 90°, 180° y 270°.

Si este tipo de técnicas se amplía aún más, PSK se puede hacer por ocho o dieciséis valores también, dependiendo de la necesidad.

Modulador BPSK

El diagrama de bloques de la clave de cambio de fase binaria consiste en el modulador de equilibrio que tiene la onda sinusoidal portadora como una entrada y la secuencia binaria como la otra entrada. La modulación BPSK se realiza mediante un modulador de equilibrio que multiplica las dos señales aplicadas a la entrada. Para una entrada binaria cero, la fase será de 0° y para una entrada alta, la inversión de fase es de 180°.

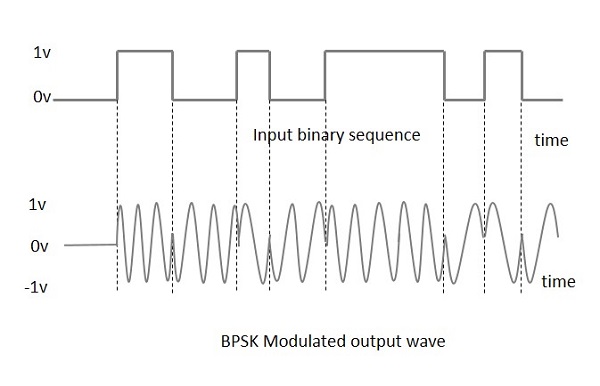

A continuación se muestra la representación diagramática de la onda de salida modulada BPSK junto con su entrada dada.

La onda sinusoidal de salida del modulador será la portadora de entrada directa o la portadora de entrada invertida (con cambio de fase de 180°), que es función de la señal de datos.

Demodulador BPSK

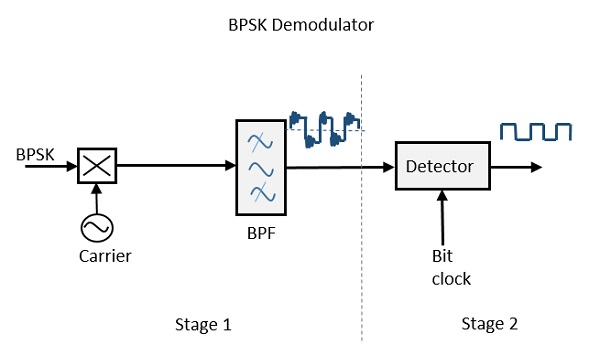

El diagrama de bloques del demodulador BPSK consta de un mezclador con circuito oscilador local, un filtro paso banda, un circuito detector de dos entradas. El diagrama es el siguiente.

Al recuperar la señal de mensaje de banda limitada, con la ayuda del circuito mezclador y el filtro de paso de banda, se completa la primera etapa de demodulación. Se obtiene la señal de banda base limitada por banda y esta señal se utiliza para regenerar el flujo de bits del mensaje binario.

En la siguiente etapa de demodulación, se necesita la velocidad de reloj de bits en el circuito detector para producir la señal de mensaje binario original. Si la tasa de bits es un submúltiplo de la frecuencia de la portadora, la regeneración del reloj de bits se simplifica. Para que el circuito sea fácilmente comprensible, también se puede insertar un circuito de decisión en la segunda etapa de detección.